# Optimizations in Symmetric Cryptography

Copyright © Ko Stoffelen, 2022

ISBN 978-94-6421-722-3

Cover design by Marilou Maes, Persoonlijk Proefschrift Printed by GVO Drukkers en Vormgevers

Where applicable, this work is licensed under the Creative Commons Attribution-NonCommercial-ShareAlike 4.0 International license. To view a copy of this license, visit https://creativecommons.org/licenses/by-nc-sa/4.0/legalcode.

## Optimizations in Symmetric Cryptography

### **Proefschrift**

ter verkrijging van de graad van doctor aan de Radboud Universiteit Nijmegen op gezag van de rector magnificus prof. dr. J.H.J.M. van Krieken, volgens besluit van het college voor promoties in het openbaar te verdedigen op

> woensdag 1 juni 2022 om 12:30 uur precies

> > door

Koos Wim Stoffelen

geboren op 7 april 1992 te Groningen

### Promotoren

prof. dr. Joan Daemen

prof. dr. Peter Schwabe

### Manuscriptcommissie

prof. dr. Bart Jacobs

prof. dr. Anne Canteaut

Inria, Frankrijk

prof. dr. ir. Vincent Rijmen

KU Leuven, België

dr. ir. Marc Stevens

Centrum Wiskunde & Informatica, Amsterdam

dr. Gilles Van Assche

STMicroelectronics, België

### Acknowledgements

This journey would not have been possible without all the great people who came along the way. First of all, I express my thanks to Peter Schwabe, my supervisor. I recall a certain dinner at an Indian restaurant, after the Operating Systems Security course, where I first learned about post-quantum cryptography and the possibility of doing a PhD with you. Neither of us would then have thought that there would be so few mentions of post-quantum cryptography in this thesis. Thanks for always being so approachable and for providing guidance whenever asked, even if it required me to go through the Chicago Manual of Style again.

I also thank the manuscript committee consisting of Bart Jacobs, Anne Canteaut, Vincent Rijmen, Marc Stevens, and Gilles Van Assche, for taking the time to go through my thesis.

Most of the work was done together with a number of brilliant coauthors whom I am grateful to for all the discussions. Thanks to Joan Daemen, Lauren De Meyer, Benjamin Grégoire, Hannes Gross, Matthias Kannwischer, Thorsten Kranz, Martin Krenn, Gregor Leander, Stefan Mangard, Kostas Papagiannopoulos, Joost Rijneveld, Peter Schwabe, and Friedrich Wiemer.

Of the utmost importance was the presence of Brinda, Christoph, Dan, Engelbert, Erik, Fabian, Freek, Guillaume, Jon, Joost, Joost, Kostas, Léo, Marc, Matthias, Michael, Niels, Pedro, Pol, Ronny, Sander, and all the other nice colleagues in and around the Digital Security group – simply too many to list exhaustively! The 'around' extends even to the Eindhoven crew that was always there. I have fond memories of the countless coffee breaks, Friday drinks, group outings, movie nights, conferences, summer schools, working groups, weddings, and other events that we have enjoyed together. These really are the things that made this PhD possible and I can not imagine what it would have been like without. A huge thanks to all of you!

I thank Nick, Kris, and Alex of the Cloudflare crypto team for taking me on as an intern and for the valuable experience in London and San Francisco.

Next I am grateful to 't Haasje for keeping me somewhat in shape, for being able to empty my mind during practice, for challenging competitions, but mostly for many fun events with its very enthusiastic members.

Then there is the Wijnnadeeltjes crew with whom I have shared many crazy adventures over at least as many drinks. Now spread out over the country and somewhat more mature, but may we continue doing this for a long time. Thanks!

From way back, thanks to Raphaël and Léon for being great friends for so long, regardless of how many times our lives have changed. It is hard to express how appreciated that is.

Finally, I thank my family for their love and support. We have shared many celebrations of life, but more importantly, you have always been there when we had to deal with the difficulties of life. Thanks to all of you.

| A | cknov           | wledge | ments                                          | v   |  |  |  |  |

|---|-----------------|--------|------------------------------------------------|-----|--|--|--|--|

| 1 | 1 Introduction  |        |                                                |     |  |  |  |  |

|   | 1.1             | Outlin | ne and Contributions                           | 2   |  |  |  |  |

|   | 1.2             | Resear | rch Data Management                            | 7   |  |  |  |  |

| 2 | Preliminaries 9 |        |                                                |     |  |  |  |  |

|   | 2.1             | Mathe  | ematics                                        | 9   |  |  |  |  |

|   | 2.2             | Symm   | netric Cryptology                              | 11  |  |  |  |  |

|   |                 | 2.2.1  | Idealized Abstractions                         | 11  |  |  |  |  |

|   |                 | 2.2.2  | Primitives                                     | 12  |  |  |  |  |

|   |                 | 2.2.3  | AES                                            | 13  |  |  |  |  |

|   | 2.3             | Crypt  | ographic Implementations                       | 14  |  |  |  |  |

|   |                 | 2.3.1  | Assembly                                       | 14  |  |  |  |  |

|   |                 | 2.3.2  | ARM Cortex-M                                   | 15  |  |  |  |  |

|   |                 | 2.3.3  | ARM Cortex-A and NEON                          | 15  |  |  |  |  |

|   |                 | 2.3.4  | RISC-V                                         | 16  |  |  |  |  |

|   | 2.4             | Side-C | Channel Attacks and Countermeasures            | 16  |  |  |  |  |

|   |                 | 2.4.1  | Timing Attacks                                 | 17  |  |  |  |  |

|   |                 | 2.4.2  | Power and Electromagnetic Attacks              | 18  |  |  |  |  |

| Ι | Cry             | yptogi | raphic Building Blocks                         | 21  |  |  |  |  |

| 3 | S-bo            | oxes   |                                                | 23  |  |  |  |  |

|   | 3.1             | Introd | luction                                        | 23  |  |  |  |  |

|   | 3.2             | Shorte | est Linear Straight-Line Programs              | 25  |  |  |  |  |

|   | 3.3             | Optim  | nizing S-box Implementations using SAT Solvers | 27  |  |  |  |  |

|   |                 |        |                                                | vii |  |  |  |  |

|   |     | 3.3.1           | Notation                                              | 29 |  |  |  |

|---|-----|-----------------|-------------------------------------------------------|----|--|--|--|

|   |     | 3.3.2           | Optimizing for Multiplicative Complexity              | 29 |  |  |  |

|   |     | 3.3.3           | Optimizing for Bitslice Gate Complexity               | 33 |  |  |  |

|   |     | 3.3.4           | Optimizing for Gate Complexity                        | 36 |  |  |  |

|   |     | 3.3.5           | Optimizing for Depth Complexity                       | 37 |  |  |  |

|   | 3.4 | Comb            | oining Criteria: Optimizing the PRIMATEs S-box        | 40 |  |  |  |

|   | 3.5 | Concl           | usion                                                 | 43 |  |  |  |

| 4 | MD  | S Matr          | rices                                                 | 45 |  |  |  |

|   | 4.1 | Introd          | luction                                               | 45 |  |  |  |

|   | 4.2 | Prelin          | ninaries                                              | 49 |  |  |  |

|   |     | 4.2.1           | Basic Notations                                       | 49 |  |  |  |

|   |     | 4.2.2           | MDS Constructions                                     | 51 |  |  |  |

|   |     | 4.2.3           | Specially Structured Matrix Constructions             | 52 |  |  |  |

|   | 4.3 | .3 Related Work |                                                       |    |  |  |  |

|   |     | 4.3.1           | Local Optimizations                                   | 56 |  |  |  |

|   |     | 4.3.2           | Global Optimizations                                  | 58 |  |  |  |

|   | 4.4 | Result          | ts                                                    | 61 |  |  |  |

|   |     | 4.4.1           | Improved Implementations of Matrices                  | 61 |  |  |  |

|   |     | 4.4.2           | Statistical Analysis                                  | 65 |  |  |  |

|   |     | 4.4.3           | Best results                                          | 70 |  |  |  |

| 5 | Col | umn-Pa          | arity Mixers                                          | 75 |  |  |  |

|   | 5.1 | Introduction    |                                                       |    |  |  |  |

|   |     | 5.1.1           | Our Contributions                                     | 77 |  |  |  |

|   | 5.2 | Colun           | nn-Parity Mixers and their Properties                 | 78 |  |  |  |

|   |     | 5.2.1           | Matrices                                              | 78 |  |  |  |

|   |     | 5.2.2           | Definition of Column-Parity Mixers                    | 79 |  |  |  |

|   |     | 5.2.3           | Group Properties                                      | 81 |  |  |  |

|   |     | 5.2.4           | The Special Case of Circulant Parity-Folding Matrices | 82 |  |  |  |

|    |                | 5.2.5     | Computational Cost                          | 83  |

|----|----------------|-----------|---------------------------------------------|-----|

|    | 5.3            | Propa     | gation of Linear Masks                      | 84  |

|    |                | 5.3.1     | Linear Propagation in Iterated Permutations | 84  |

|    |                | 5.3.2     | Mask Propagation in Column-Parity Mixers    | 86  |

|    | 5.4            | Diffus    | ion Properties                              | 87  |

|    |                | 5.4.1     | The Column-Parity Kernel                    | 88  |

|    |                | 5.4.2     | Propagation of Isolated Bits                | 91  |

|    |                | 5.4.3     | Comparison to Other Mixing Layers           | 92  |

|    | 5.5            | A Gen     | neral Design Strategy                       | 93  |

|    |                | 5.5.1     | Structure of the Round Function             | 93  |

|    |                | 5.5.2     | Outline of the Steps in our Design Approach | 95  |

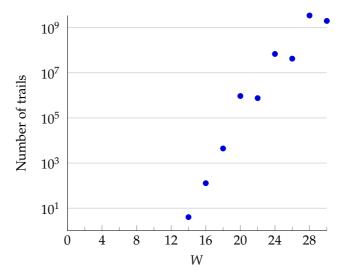

|    |                | 5.5.3     | Searching Linear and Differential Trails    | 97  |

|    | 5.6            | The M     | lixifer Permutation                         | 103 |

|    |                | 5.6.1     | Design Goals                                | 103 |

|    |                | 5.6.2     | The Construction                            | 104 |

|    |                | 5.6.3     | Evaluation                                  | 109 |

|    |                | 5.6.4     | The Number of Rounds                        | 118 |

|    |                | 5.6.5     | Implementation Cost                         | 119 |

|    |                | 5.6.6     | Comparing to Other Ciphers                  | 121 |

|    | 5.7            | Concl     | usions and Future Work                      | 122 |

|    |                |           |                                             |     |

| II | Oı             | ntimiz    | zed Implementations                         | 125 |

|    | O <sub>1</sub> | V 1111112 | acu implementations                         | 120 |

| 6  | ARN            | A Corte   | ex-M                                        | 127 |

|    | 6.1            | Introd    | luction                                     | 127 |

|    | 6.2            | Prelim    | ninaries                                    | 129 |

|    |                | 6.2.1     | Implementing AES                            | 129 |

|    |                | 6.2.2     | ARM Cortex-M                                | 130 |

|    |                | 6.2.3     | Accelerating Memory Access                  | 131 |

|    | 6.3            | Makin     | ng AES Fast                                 | 133 |

|    |                |           |                                             |     |

|   |     | 6.3.1  | Our Implementations                       | 135 |

|---|-----|--------|-------------------------------------------|-----|

|   |     | 6.3.2  | Comparison to Previous Implementations    | 136 |

|   |     | 6.3.3  | Benchmarking with FELICS                  | 137 |

|   | 6.4 | Protec | cting against Timing Attacks              | 138 |

|   |     | 6.4.1  | Our Implementation                        | 139 |

|   | 6.5 | Protec | cting against Side-Channel Attacks        | 142 |

|   |     | 6.5.1  | Our Implementation                        | 143 |

|   |     | 6.5.2  | Comparison to Previous Implementations    | 144 |

|   | 6.6 | Concl  | usion and Outlook                         | 145 |

| 7 | RIS | CV     |                                           | 147 |

| , | 7.1 |        | luction                                   | 147 |

|   | 7.1 |        | ISC-V Architecture                        | 149 |

|   | 7.2 | 7.2.1  | The RV32I Base Instruction Set            | 149 |

|   |     | 7.2.1  | Standardized Extensions                   | 151 |

|   |     | 7.2.2  |                                           | 151 |

|   | 7.0 |        | Benchmarking Platform                     |     |

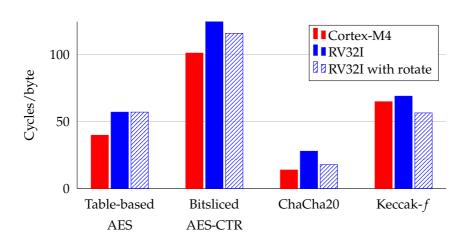

|   | 7.3 |        | Table best distributed for                | 153 |

|   |     | 7.3.1  | Table-based Implementations               | 154 |

|   | - 4 | 7.3.2  | Bitsliced Implementations                 | 155 |

|   | 7.4 |        | ha                                        | 157 |

|   |     | 7.4.1  | Result                                    | 157 |

|   | 7.5 |        | k                                         | 158 |

|   |     | 7.5.1  | Efficient Scheduling                      | 158 |

|   |     | 7.5.2  | Bit Interleaving                          | 158 |

|   |     | 7.5.3  | Lane Complementing                        | 159 |

|   |     | 7.5.4  | Result                                    | 159 |

|   | 7.6 | Arbitı | rary-Precision Arithmetic                 | 160 |

|   |     | 7.6.1  | Carries and Reduced-Radix Representations | 160 |

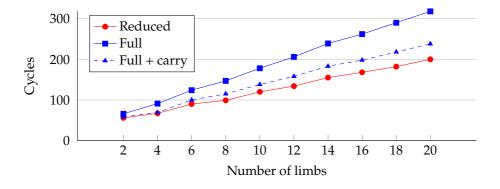

|   |     | 7.6.2  | Addition                                  | 161 |

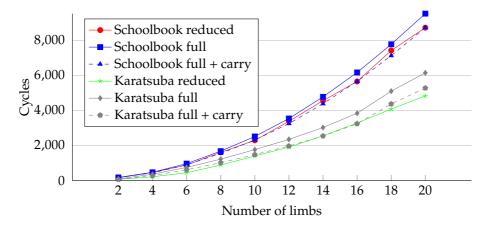

|   |     | 7.6.3  | Schoolbook Multiplication                 | 162 |

|    |      | 7.6.4   | Karatsuba Multiplication               | 163 |

|----|------|---------|----------------------------------------|-----|

|    | 7.7  | Exten   | ding RISC-V and Discussion             | 164 |

|    |      | 7.7.1   | Speed Comparison with ARM Cortex-M4    | 164 |

|    |      | 7.7.2   | The RISC-V B Extension                 | 166 |

|    |      | 7.7.3   | Number of Registers                    | 168 |

|    |      | 7.7.4   | Carry Flag                             | 168 |

|    | 7.8  | Concl   | usion                                  | 169 |

|    |      |         |                                        |     |

| II | I S  | ide-C   | hannel Countermeasures                 | 171 |

| 8  | Vect | orizati | on                                     | 173 |

|    | 8.1  | Introd  | luction                                | 173 |

|    | 8.2  | Prelin  | ninaries                               | 175 |

|    |      | 8.2.1   | Higher-Order Masking of AES            | 175 |

|    |      | 8.2.2   | Strong Non-interference                | 176 |

|    |      | 8.2.3   | Bounded-Moment Leakage Model           | 177 |

|    |      | 8.2.4   | Vectorization with NEON                | 178 |

|    | 8.3  | Vector  | rizing Masking of AES                  | 179 |

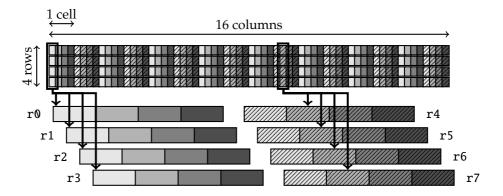

|    |      | 8.3.1   | Representing the Masked State          | 179 |

|    |      | 8.3.2   | Parallel Multiplication and Refreshing | 180 |

|    |      | 8.3.3   | SubBytes                               | 185 |

|    |      | 8.3.4   | Linear Layer                           | 186 |

|    |      | 8.3.5   | Performance                            | 187 |

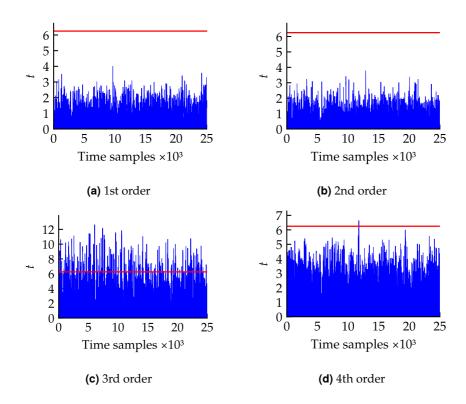

|    | 8.4  | Side-C  | Channel Evaluation                     | 190 |

|    |      | 8.4.1   | Measurement Setup                      | 190 |

|    |      | 8.4.2   | Security Order Evaluation              | 191 |

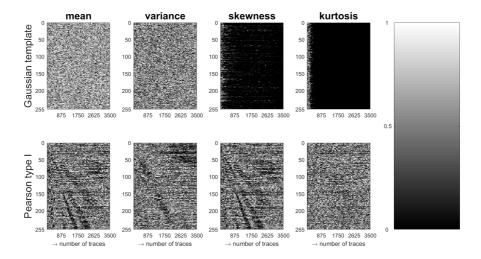

|    |      | 8.4.3   | Information-Theoretic Evaluation       | 195 |

|    | 8.5  | Concl   | usion and Outlook                      | 197 |

| 9   | Reu    | sing Ra                       | andomness                                          | 199 |

|-----|--------|-------------------------------|----------------------------------------------------|-----|

|     | 9.1    | Introd                        | luction                                            | 199 |

|     | 9.2    | ing without Online Randomness | 201                                                |     |

|     |        | 9.2.1                         | Computation on Masked Data                         | 203 |

|     |        | 9.2.2                         | Application to Nonlinear Gates                     | 206 |

|     |        | 9.2.3                         | Construction of a New Masked AND                   | 208 |

|     | 9.3    | Synth                         | esis of First-Order Secure Implementations         | 215 |

|     | 9.4    | Maski                         | ing AES                                            | 218 |

|     |        | 9.4.1                         | SubBytes                                           | 219 |

|     |        | 9.4.2                         | Linear Components                                  | 220 |

|     |        | 9.4.3                         | Results                                            | 222 |

|     | 9.5    | Discu                         | ssion                                              | 222 |

|     |        | 9.5.1                         | Comparison to Previous Work                        | 222 |

|     |        | 9.5.2                         | Randomness in Perspective                          | 225 |

|     |        | 9.5.3                         | Hardware                                           | 227 |

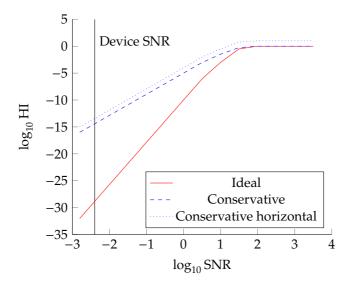

|     | 9.6    | Securi                        | ity Analysis                                       | 229 |

|     |        | 9.6.1                         | Formal Verification in the <i>t</i> -Probing Model | 229 |

|     |        | 9.6.2                         | Horizontal Attacks                                 | 231 |

|     |        | 9.6.3                         | Beyond the <i>t</i> -Probing Model                 | 235 |

|     | 9.7    | Concl                         | usions and Future Work                             | 236 |

| 10  | Con    | clusior                       | ns and Outlook                                     | 239 |

| Bil | bliog  | raphy                         |                                                    | 243 |

| Su  | mma    | ry                            |                                                    | 277 |

| Sa  | menv   | atting                        |                                                    | 279 |

| Cu  | ırricu | ılum V                        | itae                                               | 281 |

## Chapter 1

### Introduction

Let me start with the title of this thesis. The title *Optimizations in Symmetric Cryptography* is only four words long, yet it expresses in a very compact way what this thesis is all about. To introduce this thesis and the topics that it contains, we can use the title and slowly unravel it word by word. For pedagogical reasons, it makes most sense to start on the right-hand side and move to the left.

The first and arguably the most important word that needs to be understood is *Cryptography*. History is filled with stories where protection of information plays a pivotal role. Whether this information concerns military operations, as with the invasion of Greece by the Achaemenid Empire under Xerxes I in the fifth century BC, or love letters, as between queen Marie Antoinette of France and count Axel von Fersen of Sweden, is of little interest here. Since long before the term 'cryptography' (or 'cryptology') was first coined, there have been people who tried to hide information by scrambling messages and there have been people who tried to decode these scrambled messages.

This is not any different from today's situation. In fact, protection of information may be more pivotal than ever in a largely digitalized society. What have changed considerably throughout history are the cryptographic methods that are used to scramble messages and the cryptanalytic methods that are used to decode messages. Modern-day cryptography is a lot more rigorous, mathematically speaking. Publicly available scrutiny of cryptographic systems has significantly improved the security of the systems we use today, despite more powerful attackers. Another trend is that modern-day cryptography has become more versatile: it considers more properties than only the confidentiality of information. For example, it can also give guarantees that a message was not modified in transit or who sent a particular message.

Now is a good moment to move to the next word of the title. The adjective *Symmetric* refers to a particular branch of cryptography. The confidentiality of an encrypted message usually depends on a cryptographic key and only the holder of this key should be able to decrypt the message. For some historical cryptographic systems this key may have been a code word, agreed in advance by the relevant parties. Nowadays that key is usually a string of ones and zeroes. When the same key is used to encrypt and to decrypt a message, this is a symmetric cryptographic system. This is unlike asymmetric cryptography, also called public-key cryptography, which was first realized in the 1970s. In public-key encryption, the key that is used to decrypt a message is different but mathematically related to the key that is used to encrypt a message. However, we need not submerge ourselves into this too much as this thesis only concerns symmetric cryptography.

Assuming that nobody will argue against skipping the preposition *in*, that just leaves *Optimizations*. This term is sufficiently vague that it spans across all core chapters of this thesis. Its use should immediately raise a few questions, such as what, why, and how. The how definitely goes too far for the introduction, so let's leave that for later chapters. The answers to what and why partially follow from the notion that adding cryptography always comes with certain costs. These costs can be any combination of more CPU cycles, more gates in an integrated circuit, more electrical energy required, more code complexity, and so on. Lowering these costs may lead to even more widespread use of cryptography, improving the security of information. Of course, it is an equally true statement that many computer scientists and mathematicians just like optimization problems.

#### 1.1 Outline and Contributions

The core chapters of this thesis are based on a sequence of published papers. These papers contain contributions to multiple sub-areas in cryptographic research. While they are certainly related, it felt natural to categorize the work into three parts.

The chapters in Part I focus on building blocks that are used in the design of round functions of iterated cryptographic permutations and ciphers. The aim is to improve these small building blocks such that they increase the security of the complete scheme as much as possible using as few operations as possible. The three chapters study three types of cryptographic building blocks: S-boxes, maximum-distance separable matrices, and column-parity mixers.

Part II continues to optimize cryptographic permutations and ciphers, but at a different level. Once a scheme has been designed, it has to be implemented before it can be used in practice. This part covers hand-optimized software implementations in assembly language for two CPU architectures. Naturally, the choices that are made at the design stage of a permutation or cipher have a large impact on what one can do on the implementation level and, the other way around, design choices are typically made with software and/or hardware implementations in mind.

Finally, the chapters in Part III consider the common model where an attacker has access to a physical device and attempts to extract secret information, such as a secret key, using information provided by measurements of physical characteristics of that device, such as its power consumption. These information streams are called side channels. Masking is a well-studied countermeasure against this type of attacker, but it tends to be a costly one: implementations become much slower and/or bigger. The chapters in this part improve this with two different approaches. Once more, there is some interaction going on. Choices made during both the design and the implementation phases of a cipher impact the cost of applying side-channel countermeasures. Design and implementation choices can also be made with the cost of side-channel countermeasures in mind.

All core chapters are based on published papers with minor modifications. These modifications are mostly to make tables and figures fit within the dimensions of the current page size and to make the style and formatting more uniform. Some overlapping preliminaries have been moved to Chapter 2 to improve the flow for the reader. In a few cases, the scientific content has been updated, shortened, or otherwise modified. Such modifications are detailed at the beginning of the respective chapters.

Most chapters are based on joint work with various great coauthors. To clarify my personal contributions, I will describe per chapter what forms the basis of the chapter and how I contributed to it.

### Chapter 3: S-boxes

This chapter is based on the following publication.

Ko Stoffelen. "Optimizing S-Box Implementations for Several Criteria Using SAT Solvers". In: *Fast Software Encryption – FSE 2016*. Vol. 9783. Lecture Notes in Computer Science. Springer, Heidelberg, Mar. 2016, pp. 140–160.

All work that is described in this publication is my own. The results on the multiplicative complexity of S-boxes were obtained while I was writing my Master's thesis [Sto15] under supervision of Lejla Batina. The work on all other optimization criteria, including the part on combining optimization criteria, was carried out as part of my PhD. The parts on multiplicative complexity, although technically not a part of my PhD, are only included for completeness.

### Chapter 4: MDS Matrices

This chapter is based on the following publication.

Thorsten Kranz, Gregor Leander, Ko Stoffelen, and Friedrich Wiemer. "Shorter Linear Straight-Line Programs for MDS Matrices". In: *IACR Transactions on Symmetric Cryptology* 2017.4 (2017), pp. 188–211.

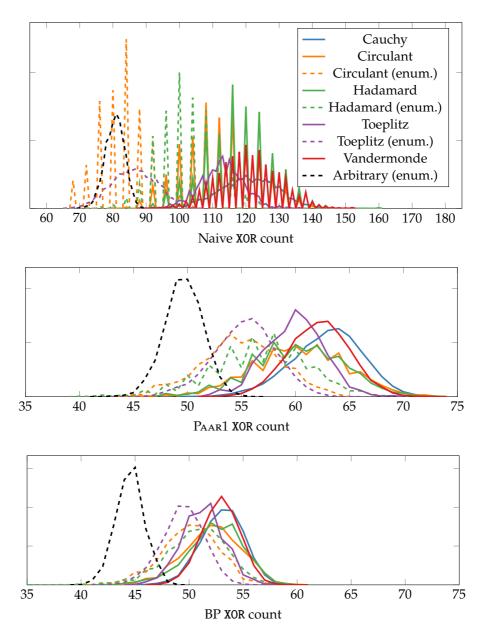

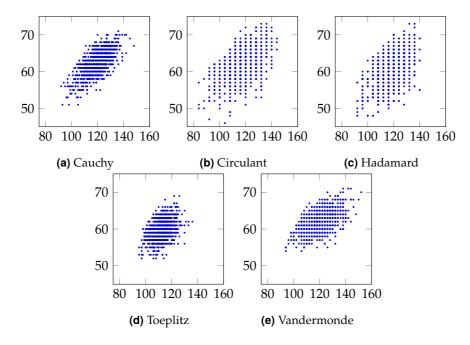

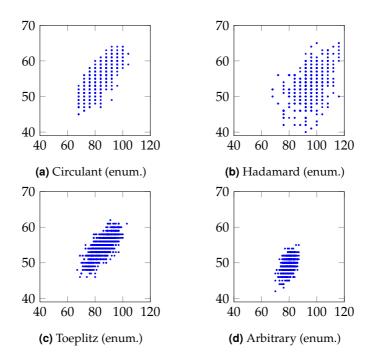

The work was a collaboration effort. Personally I worked on implementations of variants of what we call the BP heuristics and I ran many experiments. I

also wrote parts of the paper and contributed to discussions. The results from the statistical analysis and the correlation figures were produced by Friedrich Wiemer and Thorsten Kranz.

### Chapter 5: Column-Parity Mixers

This chapter is based on the following publication.

Ko Stoffelen and Joan Daemen. "Column Parity Mixers". In: *IACR Transactions on Symmetric Cryptology* 2018.1 (2018), pp. 126–159.

The work was a collaboration effort. Personally I contributed to the development of the theory on column-parity mixers and their diffusion properties, the general design strategy, the Mixifer permutation and its security analysis, its software implementations, and to writing the paper. The work for the subsections on linear mask propagation, trail clustering, and on impossible differential cryptanalysis was done by Joan Daemen.

### Chapter 6: ARM Cortex-M

This chapter is based on the following publication.

Peter Schwabe and Ko Stoffelen. "All the AES You Need on Cortex-M3 and M4". In: *SAC 2016: 23rd Annual International Workshop on Selected Areas in Cryptography.* Vol. 10532. Lecture Notes in Computer Science. Springer, Heidelberg, Aug. 2016, pp. 180–194.

The work was a collaboration effort. Personally I wrote all the code and I wrote most of the paper.

#### Chapter 7: RISC-V

This chapter is based on the following publication.

Ko Stoffelen. "Efficient Cryptography on the RISC-V Architecture". In: *LATINCRYPT 2019: 6th International Conference on Cryptology and Information Security in Latin America*. Vol. 11774. Lecture Notes in Computer Science. Springer, Heidelberg, Sept. 2019, pp. 323–340.

All work that is described in this publication is my own.

### Chapter 8: Vectorization

This chapter is based on the following publication.

Benjamin Grégoire, Kostas Papagiannopoulos, Peter Schwabe, and Ko Stoffelen. "Vectorizing Higher-Order Masking". In: *COSADE 2018: 9th International Workshop on Constructive Side-Channel Analysis and Secure Design*. Vol. 10815. Lecture Notes in Computer Science. Springer, Heidelberg, Apr. 2018, pp. 23–43.

The work was a collaboration effort. Personally I wrote the optimized implementations, helped with the lab setup, and wrote large parts of the paper. The side-channel evaluation was done by Kostas Papagiannopoulous and the new SNI refreshing and multiplication gadgets were contributed by Benjamin Grégoire.

#### Chapter 9: Reusing Randomness

This chapter is based on the following publication.

Hannes Gross, Ko Stoffelen, Lauren De Meyer, Martin Krenn, and Stefan Mangard. "First-Order Masking with Only Two Random Bits". In: *Proceedings of ACM Workshop on Theory of Implementation Security*. TIS'19. ACM, 2019, pp. 10–23.

The work was a collaboration effort. A previous version of the AND gate and some results for hardware implementations were already put on IACR ePrint by the other authors before I joined. Since then, the work has changed direction and improved results considerably. Personally, I wrote the masked AES implementation, wrote parts of the paper, performed lab and simulator experiments, and contributed to discussions.

### 1.2 Research Data Management

Nearly all software and data that were used or produced for this thesis are available in online repositories that are publicly accessible. Unless a clearly marked license file in a repository states otherwise, copyrights and related rights are waived with the Creative Commons Zero v1.0 Universal waiver. This maximizes the potential for reuse of the software and data in the future.

References to the repositories are provided throughout this thesis, but they are also summarized in this section to make them easier to find.

S-box optimization tool

https://github.com/Ko-/sboxoptimization

Shorter linear SLPs for MDS matrices

https://github.com/rub-hgi/shorter\_linear\_slps\_for\_mds\_matrices

Column-parity mixer trail search tool

https://github.com/Ko-/cpm

Mixifer implementations

https://github.com/Ko-/mixifer

AES implementations for ARM Cortex-M3 and M4

https://github.com/Ko-/aes-armcortexm

Implementations of cryptographic primitives for RV32I

https://github.com/Ko-/riscvcrypto

Masked AES implementations parallelized with vectorization https://github.com/Ko-/aes-masked-neon

Masking with two random bits https://github.com/LaurenDM/TwoRandomBits

In addition to the software and data referred to above, side-channel trace sets exist related to Chapter 8 and Chapter 9. These are not available online due to their large sizes. Instead, they are locally stored on a hard disk drive in the side-channel lab of the Digital Security group at Radboud University and will remain available upon request.

### **Preliminaries**

This chapter aims to provide some background information on symmetric cryptology and on closely-related scientific areas. This is also where we establish some notation commonly used in subsequent chapters. This chapter is by no means a complete account of everything that there is to know about the topics that are discussed, but it merely intends to cover the common ground that is required for other chapters. In those other chapters, these preliminaries are supplemented with information that is more relevant to a specific chapter. Still, the reader is referred to a proper textbook or a course if the reader desires information that is not covered here.

This chapter first explains some basic mathematical concepts in Section 2.1. It then proceeds with the fundamentals of symmetric cryptology in Section 2.2. Section 2.3 puts cryptographic algorithms into a physical device, such as a microcontroller, and explains why implementations are also scientifically interesting. Finally, Section 2.4 discusses pitfalls of cryptographic implementations, how they can be attacked, and how these attacks can be prevented.

#### 2.1 Mathematics

Most constructs in cryptology use existing and well-understood concepts from number theory, algebra, and other branches of mathematics. This makes it easier to reason about these constructs and therefore to study their security properties, which is what cryptographers are usually interested in. It is assumed that the reader is familiar with basic linear algebra, probability theory, predicate logic and common algebraic structures. Nonetheless, some definitions are available here as a reference.

A set S is a collection of unique objects, such as different numbers. An object a is an *element* of a set S, denoted  $a \in S$ , when it is one of the objects in the collection. A set can be specified by listing its objects  $\{a,b,c,d,\ldots\}$ , but that can get quite lengthy when a set contains an infinite number of objects. Some commonly used sets also have special names. For example,  $\mathbb{Z}$  is the set of integers and  $\mathbb{N}$  is the set of natural numbers. In order to avoid ambiguity,  $0 \in \mathbb{N}$  in this thesis.

A *group*  $(G, \cdot)$  is an algebraic structure that is given by a set G and a binary operation  $\cdot : G \times G \to G$  that satisfies three criteria:

- ► Associativity:  $\forall a, b, c \in G : (a \cdot b) \cdot c = a \cdot (b \cdot c)$ .

- ▶ *Identity element*:  $\exists e \in G : e \cdot a = a \cdot e = a$ . This element *e* is unique.

- ▶ *Inverse element*:  $\forall a \in G : \exists b \in G : a \cdot b = b \cdot a = e$ . This *b* is called the inverse of *a* and denoted  $a^{-1}$ .

An example of a group is  $(\mathbb{Z}, +)$ , where + is addition of integers. For this additive example, inverses are denoted -a. A group  $(G, \cdot)$  is *Abelian* when  $\cdot$  is also commutative:  $\forall a, b \in G : a \cdot b = b \cdot a$ .

A straightforward extension of groups adds another operation. A *ring*  $(R, +, \cdot)$  is an algebraic structure where the following criteria hold:

- $\blacktriangleright$  (R, +) is an Abelian group.

- $\triangleright$  · is associative over *R* and has a (multiplicative) identity element.

- ▶ Distributivity:  $\forall a, b, c \in R : a \cdot (b+c) = (a \cdot b) + (a \cdot c) \land (a+b) \cdot c = (a \cdot c) + (b \cdot c)$ .

An example of a ring is  $(\mathbb{Z}, +, \cdot)$ , where + and  $\cdot$  are addition and multiplication of integers, respectively.

A *commutative ring* is a ring where the multiplication operation  $\cdot$  is also commutative. A *field* is a commutative ring where every element of its set also has a multiplicative inverse under the multiplication operation  $\cdot$ . A group, ring,

and field are *finite* when their set has a finite number of elements. In (symmetric) cryptology, finite fields are common algebraic structures.

The *order* of a finite field, often denoted by q, is defined as the number of elements in its set. A finite field of a certain order q exists if and only if q is some power of a prime number, i. e.,  $q = p^k$  with k a positive integer. Then p is also known as the *characteristic* of the field. In general, there are many ways to construct a finite field with a specific order q, but they are all isomorphic. Intuitively, this means that finite fields of equal order behave the same with respect to calculations, as there exist reversible mappings between them. This is why explicit constructions are sometimes ignored and one just speaks of 'the' finite field  $\mathbb{F}_q$ . The smallest finite field is the field with 2 elements, denoted  $\mathbb{F}_2$ , which can be used to model bits with XOR and AND operations.

### 2.2 Symmetric Cryptology

In this section we cover several cryptographic primitives that most cryptographic schemes in symmetric cryptology are built upon. Before we discuss these primitives, the properties that they provide, and some examples, we look at idealized abstractions that model the properties that we desire. Finally, we discuss one instantiation of a cryptographic primitive, AES, in more detail as it will occur in multiple chapters of this thesis.

#### 2.2.1 Idealized Abstractions

The first notion is that of a *pseudorandom permutation* (PRP). In general, a permutation is a bijective function from some set to itself. A PRP  $f: X \to X$  is a permutation f from some set X to itself, such that it cannot be distinguished with non-negligible probability from a permutation that is selected uniformly at random from the set of all permutations over X. More commonly, a PRP is defined using a PRP family  $f: K \times X \to X$ , where there is some key space K

and for every  $k \in K$  it holds that  $f(k, \cdot)$  is a PRP. It is usually required that f and  $f^{-1}$  are efficiently computable.

A more general notion is that of a *pseudorandom function* (PRF). The difference is that a PRF does not require that the function maps a set to itself, but it allows an arbitrary output set. Consequently, it does not need to be a bijective mapping and it may not have an inverse. Clearly, every PRP is also a PRF.

Such idealized abstractions are useful in security proofs. They also clarify what properties a particular instantiation of a cryptographic primitive should have.

#### 2.2.2 Primitives

Arguably one of the simplest primitives is the (unkeyed) *cryptographic permutation*. This is a function  $P: \{0,1\}^n \to \{0,1\}^n$  that processes fixed-length blocks such that P is a PRP. Typical examples are the Keccak-f permutations [BDPV11b].

Block ciphers also process fixed-length blocks, but add a fixed-length key. More precisely, a block cipher consists of an encryption function  $E:\{0,1\}^{|k|}\times\{0,1\}^n\to\{0,1\}^n$  and a decryption function  $D:\{0,1\}^{|k|}\times\{0,1\}^n\to\{0,1\}^n$  such that for all  $k\in\{0,1\}^{|k|}$  and  $x\in\{0,1\}^n$ , D(k,E(k,x))=x. A secure block cipher is a family of PRPs. A block cipher can be constructed from a cryptographic permutation [EM93], but direct instantiations of block ciphers are more common. The prime example of a block cipher that is heavily used today is AES. We will discuss its construction in more detail in the Section 2.2.3.

A downside of a block cipher is that one can only use the encryption or decryption function once there is an input of precisely *n* bits. *Stream ciphers* are more flexible and allow inputs of arbitrary length or at least arbitrary multiples of some block length. Stream ciphers can be constructed from block ciphers by putting the block cipher in a so-called mode of operation. AES-CTR is a stream cipher that works like this. They can also be constructed directly, such as the ChaCha ciphers [Ber08a].

A *cryptographic hash function*, or simply hash function in the context of this thesis, is another primitive that is used in many cryptographic schemes. A hash function is an efficiently-computable function  $h: \{0,1\}^* \to \{0,1\}^n$  that maps arbitrary-length inputs to fixed-length outputs. h needs to satisfy the following additional criteria:

- ▶ *Pre-image resistance*: given y = h(x), it should be hard to find any x' such that h(x') = y.

- ▶ Second pre-image resistance: given x, it should be hard to find any  $x' \neq x$  such that h(x) = h(x').

- ► *Collision resistance*: it should be hard to find any x, x' with  $x \neq x'$  such that h(x) = h(x').

Typical examples are the SHA-2 [NIS15a] and SHA-3 [NIS15b] hash functions.

#### 2.2.3 AES

In this section we zoom in on one particular block cipher, as it appears in all chapters of this thesis. In 1997, NIST announced that they were looking for a successor to DES [DES77] and they put out a call for proposals for new ciphers. All submissions were to be block ciphers that support a block length of 128 bits and key sizes of 128, 192, and 256 bits. Out of fifteen submissions, Rijndael was selected as the winner and it was finally standardized as AES in 2001 [DR02].

The AES design is based on a number of rounds, where each round consists of a nonlinear substitution of the bytes of the state, followed by linear operations that aim to spread and mix parts of the state, followed by the addition of a round key that is derived from the key through a key schedule. These steps are called SubBytes, ShiftRows, MixColumns, and AddRoundKey in that order. The first round starts with an initial AddRoundKey and the final round is different by omitting MixColumns as it does not improve security anymore. AES-128,

the variant with a key size of 128 bits, has 10 rounds, AES-192 12 rounds, and AES-256 14 rounds.

The security of AES has been established through years of thorough cryptanalysis. An attack that is always possible is brute-force search for the correct key. The amount of effort that this costs is determined by the size of the key, so for AES-128 this takes 2<sup>128</sup> AES operations (or 2<sup>127</sup> on average). Linear [Mat94] and differential [BS91] cryptanalysis are general methods that apply to all block ciphers and have proved themselves to be powerful attacks in the past. However, AES was designed with these attacks in mind and its designers have proven that these attacks require much more effort than brute-force search.

Currently, the best-known attack against AES-128, conveniently ignoring related-key attacks for the moment, is a biclique attack that requires 2<sup>126.13</sup> operations and 2<sup>56</sup> bits or 9 petabyte of storage [TW15]. Although this implies a theoretical break of AES, in practice, the biclique attack is unlikely to be faster than simple brute-force search of the key.

AES is widely deployed and used in many products, protocols, and industries to securely encrypt data.

### 2.3 Cryptographic Implementations

Cryptographic algorithms are implemented in a wide range of hardware and software. A very rough division can be made between ASICs, FPGAs, microcontrollers, smartphones, high-end CPUs, and GPUs. The topics in this thesis primarily consider the middle part of this range.

### 2.3.1 Assembly

A lot of cryptographic implementations are written in assembly language. This has several advantages. First of all, the implementation is likely to be faster. This is especially useful if the operation is to be performed many times. A

human with knowledge of the mathematical properties of the cryptographic algorithm can think of optimizations that are beyond what generic compilers can do. Also note that compilers are optimized to perform well on average, without affecting the compilation time or binary size too much. This may not be what is wanted for a cryptographic implementation. Another reason for programming in assembly is that a compiler may unknowingly alter the behavior of a program. Statements such as removing a key from memory by overwriting it with zeroes may be removed by a compiler, because it thinks it is useless if that value is not read again later.

Some disadvantages of assembly are, of course, that you lose portability between CPU architectures and that you increase the code complexity. Usually the idea is that this effort is done once in a software library and everyone else can then reuse that library.

#### 2.3.2 ARM Cortex-M

Various CPU architectures are mentioned frequently throughout this thesis, hence they are briefly described in this section. The first is a line of microprocessors called Cortex-M by ARM. This consists of a number of popular 32-bit low-cost processors for embedded applications that have been used in billions of devices. These processors generally run lightweight embedded operating systems or none at all. Although it is described as a RISC architecture, some models do come with multipliers, divide instructions, DSP instructions, and floating-point instructions. Noteworthy are the barrel-shift registers that provide free shifts and rotations of one input of arithmetic instructions.

#### 2.3.3 ARM Cortex-A and NEON

Cortex-A is a group of 32-bit and 64-bit processors that are used in smartphones, tablets, and other applications that require more performance. These typically run a full-fledged operating system such as Linux.

The NEON media processing engine or Advanced SIMD extension extends a Cortex-A processor with a 64-bit or 128-bit SIMD vector unit that can accelerate media and signal processing, but it can also be useful for parallel processing in cryptographic implementations.

#### 2.3.4 RISC-V

ARM designs processors, but they do not build them themselves. Instead, other companies purchase licenses to use their designs. The RISC-V project is about creating an open and free instruction set architecture and started originally at the University of California at Berkeley. There exist both open-source and proprietary processors that implement this instruction set architecture. There are 32-bit, 64-bit, and 128-bit variants of the instruction set, targeting a wide range of applications. It should be noted that the base contains very few instructions and that there are many standardized extensions that bring functionality such as multiplication, floating-point support, and vector operations, some of which are still in development.

#### 2.4 Side-Channel Attacks and Countermeasures

Research on cryptographic implementations not only aims to lower the costs of adding more secure cryptography, but it also aims to make the implementations themselves more secure. A theoretically secure cipher is not as useful when its implementation contains flaws that can be exploited to easily extract a secret key. The attacker may use information about physical characteristics of a particular implementation, called *side channels*. To reason about implementation security it is important to have an explicit *attacker model* that states what an attacker is allowed to do. From this it can be determined whether a model is relevant to a particular use case. For example, on a regular PC a secret key can often be retrieved by a privileged user by extracting it from memory or by attaching a debugger to an encryption process. From the perspective of

the implementation of a cryptographic operation in a desktop application, it is impossible to exclude these types of attacks without relying on assistance from special-purpose hardware. Hence an implementer may decide that this attacker model is not too relevant for their use case and accept these risks. On the other hand, a company that produces credit cards may take sophisticated side-channel attacks very seriously.

### 2.4.1 Timing Attacks

One branch of side-channel attacks uses timing information. A simple example is the case of testing whether two strings are equal by comparing them character by character and returning when a mismatch occurs. By measuring the time it takes to do this comparison, an attacker can determine at what position the strings begin to differ. This turns the hard problem of guessing the right string into the much simpler problem of guessing the right character a few times in a row. Kocher famously applied a similar idea to implementations of asymmetric cryptographic algorithms in 1996 [Koc96].

These timing attacks can be quite subtle. In 2005, Bernstein showed that full key recovery was possible against the AES implementation in OpenSSL because of the behavior of caches in CPUs [Ber05a]. The solution is the notion of *constant-time* implementations: the running time should be independent of secret values. But controlling the running time can be hard when there are many abstraction layers between the code and the physical world. Compilers may introduce timing variance in code that was intended to be constant-time for optimization purposes and even a single instruction may turn out to be less constant-time than one expected due to a hidden mechanism in complex and proprietary hardware.

Assembly implementations and publicly available documentation of hardware do help out a lot, as well as in-depth testing to the timing behavior of CPU instructions. Another direction is to put the whole cryptographic operation in a hardware circuit, such as with the AES-NI instruction set extension for Intel and AMD CPUs.

### 2.4.2 Power and Electromagnetic Attacks

Another branch of side-channel attacks uses other physical characteristics. In 1999, Kocher, Jaffe, and Jun showed how on many devices, the power consumption of the device correlates with the instructions and values that are being processed [KJJ99]. In cryptographic implementations, some of these values are supposed to be secret. However, by measuring the power consumption across a cryptographic operation, the implementation may leak the full cryptographic key. With *simple power analysis* (SPA), patterns are directly deduced from a single *trace* of measurements. Usually this is not enough to recover a key. *Differential power analysis* (DPA) is a more powerful attack that requires multiple traces and some statistics. The main idea is to guess some secret bits (for example, a byte of a round key in the case of AES) and to perform a statistical test to confirm whether the guess was correct. A notable variation is *correlation power analysis* (CPA) that uses the Pearson correlation coefficient to distinguish between a correct guess and a wrong guess [BCO04].

Similarly, simple and differential *electromagnetic analysis* are based on the fact that a current induces an electromagnetic field that can be measured by a probe [QS01]. Sometimes it is hard to measure the current going through a processor directly because of how the processor is integrated into a circuit. Its electromagnetic field may then be easier to measure. However, a downside can be that there may be more noise in the measurement of the electromagnetic field.

A high noise level can be combatted by generating more traces, but this also increases the amount of effort for an attacker. Some countermeasures against power and electromagnetic analysis are therefore based on increasing the amount of noise. The countermeasure that occurs most in this thesis is called

*masking*. This aims to break the correlation between the physical measurement and the secret value by adding randomness. Secret values are split into shares that by themselves are uniformly random. A careful implementation then performs the computation on the shares in such a way that the computation remains correct and that secret intermediate values remain uniformly random.

Power and electromagnetic analysis, as well as masking, can be extended to *higher orders*. This means that the statistical properties of multiple aspects of a signal are studied jointly. This can be approached with multivariate statistics or by first mapping the problem to a univariate problem. For masking, protection against higher-order attacks means that secret values need to be split into more shares.

# PART I

Cryptographic Building Blocks

### S-boxes

As a first cryptographic building block, we consider the nonlinear S-boxes that can be found in round functions of most iterated permutations or ciphers. This chapter introduces a technique to optimize implementations of such S-boxes for a number of optimization criteria. In comparison to the original publication [Sto16b], a few mistakes that were pointed out by Jérémy Jean are corrected. The S-boxes of RECTANGLE and its inverse were swapped and in an implementation of LAC there was a typo in a variable name. Another modification is that the appendices are omitted.

#### 3.1 Introduction

Implementations of cryptographic algorithms are typically optimized for one or multiple criteria, such as latency, throughput, power consumption, memory consumption, etc., but also criteria such as the cost of adding masking countermeasures to protect against side-channel attacks. It is worthwhile to spend time on this optimization, as the implementations are typically used many times. It is usually a hard problem to find an implementation that is actually theoretically minimal with respect to the criteria, e. g., general circuit minimization is  $\sum_{2}^{p}$ -complete [BU08]. However, for small functions this is still possible, using, for instance, SAT solvers. Especially for building blocks that can be used in multiple cryptographic algorithms, such as S-boxes, it is useful to look at methods for finding minimal implementations with respect to some given criteria.

In Section 3.2, we first discuss the simpler problem of finding minimal implementations of linear functions. We give a brief overview of methods for finding the shortest linear straight-line program.

We then move toward S-boxes and in Section 3.3 we consider known methods [CMH13; Mou15] that manage to find minimal implementations for the relevant optimization criteria of multiplicative complexity [BPP00], bitslice gate complexity [CHM11], and gate complexity. The definitions of these criteria are given in Section 3.3. We study how feasible the methods actually are by applying them to S-boxes that are used in recent cryptographic algorithms, such as several candidates in the CAESAR competition<sup>1</sup> and lightweight block ciphers. Additionally, we provide tools that allow anyone to conveniently do the same to other small S-boxes.

Then we look at another optimization criterion: the circuit-depth complexity. This is relevant in hardware implementations to decrease the delay and to be able to increase the clock frequency. We suggest a new method for encoding the circuit-depth-complexity decision problem in SAT and we show how feasible this method is in practice by providing efficient low-depth S-box implementations for Joltik [JNP15], Piccolo [SIH+11], LAC [ZWW+14], Prøst [KLL+14], and RECTANGLE [ZBL+14] in Section 3.3.5.

Section 3.4 discusses how several optimization criteria can be combined, by first optimizing the S-box used by the PRIMATEs [ABB+14] for multiplicative complexity and then for gate complexity. This is done by taking the intermediate result after optimizing for multiplicative complexity, identifying the linear parts of this, and by treating these as instances of the shortest linear straight-line program problem.

Full listings of the optimized implementations that are obtained can be found in the appendices of the original publication [Sto16b].

**Contributions presented in this chapter.** To summarize, the contributions of this chapter are:

<sup>1</sup> https://competitions.cr.yp.to/caesar.html

- ▶ implementations of the S-boxes in Ascon, ICEPOLE, Joltik/Piccolo, Keccak/Ketje/Keyak, LAC, Minalpher, Prøst, and RECTANGLE with a provably minimal number of nonlinear gates;

- a new method for encoding the circuit-depth-complexity decision problem as an instance of SAT;

- optimized and in some cases even provably minimal implementations of the S-boxes in Joltik/Piccolo, LAC, Prøst, and RECTANGLE with respect to bitslice gate complexity, gate complexity, and circuit-depth complexity;

- a method to combine multiple optimization criteria;

- an implementation of the S-box used by the PRIMATEs that is first optimized for multiplicative complexity and then for (bitslice) gate complexity;

- ▶ tools and documentation to optimize implementations of small nonlinear functions such as S-boxes using SAT solvers, with respect to multiplicative complexity, bitslice gate complexity, gate complexity, or circuit-depth complexity, as described in Section 3.4.

# 3.2 Shortest Linear Straight-Line Programs

Before tackling the optimization of S-boxes, let us restrict ourselves to linear functions and let us consider the Shortest Linear Program (SLP) problem over  $\mathbb{F}_2$ . Let A be an  $m \times n$  matrix of constants over  $\mathbb{F}_2$  and let x be a vector of n variables over  $\mathbb{F}_2$ . The SLP problem is to find the program with the smallest number of lines that computes Ax, where every program line is of a certain form.

Let *Z* be a set of variables over  $\mathbb{F}_2$ , that initially contains the input variables  $\{x_0, \ldots, x_{n-1}\}$ . Let  $z_i, z_j \in Z$ . Then every program line is of the form

$$z' := z_i + z_j.$$

After executing this program line, the new variable z' is added to the set,  $Z := Z \cup \{z'\}$ . The new variable z' can therefore be used in the next program line. The program is said to compute Ax when there exists a vector  $(z_1, \ldots, z_m) \in Z^m$  such that  $Ax = (z_1, \ldots, z_m)^{\mathsf{T}}$ .

Being able to find the shortest straight-line linear program has obvious applications to cryptology. Solving the SLP over  $\mathbb{F}_2$  is equivalent to finding the shortest circuit to compute a function using only XOR gates. Optimizing implementations of linear operations, such as MixColumns in AES and the linear components of certain implementations of SubBytes, can therefore be seen as instances of the SLP problem over  $\mathbb{F}_2$ . However, this method does not apply to nonlinear operations such as S-boxes. We show in Section 3.3 what kind of methods can be used in such cases.

**Solving the SLP problem.** Boyar, Matthews, and Peralta showed that the SLP problem over  $\mathbb{F}_2$  is NP-hard [BMP08]. Off-the-shelf SAT solvers can be used to find solutions for small instances of this problem. Fuhs and Schneider-Kamp presented a method [FS10] to encode the SLP problem as an instance of SAT and they show how this can be used to optimize the affine transformation of AES's SubBytes [FS10; FS12].

For larger instances, exact methods will quickly become infeasible. Alternatively, Boyar and Peralta published an approach to solve the SLP problem over  $\mathbb{F}_2$  based on a heuristic [BP10]. In short, the heuristic method uses a base vector set S, initialized with unit vectors for all variables in x, and a distance vector Dist that keeps track of the minimal Hamming distance to S for each row in A. Repeatedly, the sum of the pair of base vectors in S that minimizes the sum of Dist is added to S and Dist is updated, until Dist is the all-zero vector. If there is a tie between two pairs of base vectors, the pair that maximizes the Euclidean length of the new Dist vector is chosen. This algorithm makes it possible to find solutions to larger instances of the SLP problem.

# 3.3 Optimizing S-box Implementations using SAT Solvers

For nonlinear functions such as S-boxes, known approaches based on heuristics [BP10] all exploit additional algebraic structure that may be available, e.g., as for the S-box of AES. However, in general this additional structure may not exist and one may need to fall back to generic methods such as SAT solvers.

S-box implementations in both software and hardware can be optimized with SAT solvers according to several criteria. In this chapter we consider the following four optimization goals:

Multiplicative complexity. The multiplicative complexity of a function [BPP00] is defined as the smallest number of nonlinear gates with fan-in 2 required to compute this function. If we restrict our S-box implementations to the {AND, OR, XOR, NOT} operations, we only need to consider the number of ANDs and ORs. Optimizing for this goal is useful in the case of protecting against side-channel attacks using random masks, where nonlinear gates are typically more expensive to mask. There are also applications in multi-party computation and fully homomorphic encryption, where the cost of nonlinear operations is even more significant [ARS+15].

**Bitslice gate complexity.** The bitslice gate complexity of a function [CHM11] is defined as the smallest number of operations in {AND, OR, XOR, NOT} required to compute this function. This translates directly to efficient bitsliced software implementations, as on most common CPU architectures, there are no instructions for computing NAND, NOR, or XNOR immediately.

**Gate complexity.** The gate complexity of a function is defined as the smallest number of logic gates required to compute this function. Unlike for bitslice gate complexity, NAND, NOR, and XNOR gates are now also allowed. This translates to efficient hardware implementations, although the different amounts of area

required by these types of gates and the different delays still need to be taken into account. Note that we only consider gates with a fan-in of at most 2.

Circuit-depth complexity. The depth of a circuit is defined as the length of the longest paths from an input gate to an output gate. Every function can be computed by a circuit with depth 2, e.g., by expressing the function in conjunctive or disjunctive normal form. However, this can lead to very wide circuits with a lot of gates, which is typically not desirable. There is somewhat of a trade-off between circuit depth and number of gates. Still, optimizing for this goal is useful in the case of hardware implementations, to be able to decrease the total delay and therefore to be able to increase the clock frequency. Again, only gates with a fan-in of at most 2 are considered.

These criteria come with corresponding decision problems. For example, given a function f and some positive integer k, the *multiplicative-complexity decision problem* is defined as:

"Is there a circuit that implements f and that uses at most k nonlinear operations?"

The decision problems for the other three optimization goals can be defined analogously. Off-the-shelf SAT solvers can be used to solve these decision problems. When a SAT solver successfully finds a circuit for some value k but outputs UNSAT for k-1, it is proven that k is the minimum value. Note that when a SAT solver outputs SAT for some value k, it also provides a satisfying valuation that can be used to reconstruct an implementation of f.

In order to use SAT solvers to solve these decision problems, the problems first have to be encoded in logical formulas in conjunctive normal form (CNF), because that is the input format that the SAT solver requires.

#### 3.3.1 Notation

For the encoding, we use the notation of Mourouzis [Mou15]. We consider systems of multivariate equations over  $\mathbb{F}_2$ . In these equations, let

- $\triangleright$   $x_i$  be variables representing S-box inputs;

- $\blacktriangleright$   $y_i$  be variables representing S-box outputs;

- $ightharpoonup q_i$  be variables representing gate inputs;

- $\blacktriangleright$   $t_i$  be variables representing gate outputs;

- $ightharpoonup a_i$  be variables representing wiring between gates; and

- $\blacktriangleright$   $b_i$  be variables representing wiring *inside* gates. This will become more clear when they are first used in Section 3.3.3.

In the implementations the *logical connectives* are used to denote the types of operations. Let  $\land$ ,  $\lor$ ,  $\oplus$ ,  $\neg$  denote AND, OR, XOR, NOT, respectively, and let  $\uparrow$ ,  $\downarrow$ ,  $\leftrightarrow$  denote NAND, NOR, XNOR, respectively.

## 3.3.2 Optimizing for Multiplicative Complexity

Courtois, Mourouzis, and Hulme [CMH13; Mou15] suggested a method to encode the multiplicative-complexity decision problem. Let  $f: \mathbb{F}_2^n \to \mathbb{F}_2^m$  be an S-box and let k be the multiplicative complexity that we want to test for. Then first create a set of equations C in ANF consisting of:

- ▶  $\forall i \in \{0, ..., k-1\}$ :  $t_i = q_{2i} \cdot q_{2i+1}$ , to encode the k AND gates.

- ▶  $\forall i \in \{0,\ldots,2k-1\}$ :  $q_i = a_l + \left(\sum_{j=0}^{n-1} a_{l+j+1} \cdot x_j\right) + \left(\sum_{j=0}^{\left\lfloor \frac{i}{2}\right\rfloor 1} a_{l+n+j+1} \cdot t_j\right)$ , where  $l = i(n+1) + \left\lfloor \frac{i^2 2i + 1}{4} \right\rfloor$ , to encode that the inputs of the AND gates can be any linear combination of S-box inputs and previous AND-gate outputs. The single a represents an optional NOT gate.

▶  $\forall i \in \{0, ..., m-1\}$ :  $y_i = \left(\sum_{j=0}^{n-1} a_{s+j} \cdot x_j\right) + \left(\sum_{j=0}^{k-1} a_{s+n+j} \cdot t_j\right)$ , where s = 2k(n+1) + k(k-1) + i(n+k), to encode that the S-box outputs can be any linear combination of S-box inputs and AND-gate outputs.

For example, when n = m = 4 and k = 3, this leads to the following set of equations C:

$$q_{0} = a_{0} + a_{1} \cdot x_{0} + a_{2} \cdot x_{1} + a_{3} \cdot x_{2} + a_{4} \cdot x_{3}$$

$$q_{1} = a_{5} + a_{6} \cdot x_{0} + a_{7} \cdot x_{1} + a_{8} \cdot x_{2} + a_{9} \cdot x_{3}$$

$$t_{0} = q_{0} \cdot q_{1}$$

$$q_{2} = a_{10} + a_{11} \cdot x_{0} + a_{12} \cdot x_{1} + a_{13} \cdot x_{2} + a_{14} \cdot x_{3} + a_{15} \cdot t_{0}$$

$$q_{3} = a_{16} + a_{17} \cdot x_{0} + a_{18} \cdot x_{1} + a_{19} \cdot x_{2} + a_{20} \cdot x_{3} + a_{21} \cdot t_{0}$$

$$t_{1} = q_{2} \cdot q_{3}$$

$$q_{4} = a_{22} + a_{23} \cdot x_{0} + a_{24} \cdot x_{1} + a_{25} \cdot x_{2} + a_{26} \cdot x_{3} + a_{27} \cdot t_{0} + a_{28} \cdot t_{1}$$

$$q_{5} = a_{29} + a_{30} \cdot x_{0} + a_{31} \cdot x_{1} + a_{32} \cdot x_{2} + a_{33} \cdot x_{3} + a_{34} \cdot t_{0} + a_{35} \cdot t_{1}$$

$$t_{2} = q_{4} \cdot q_{5}$$

$$y_{0} = a_{36} \cdot x_{0} + a_{37} \cdot x_{1} + a_{38} \cdot x_{2} + a_{39} \cdot x_{3} + a_{40} \cdot t_{0} + a_{41} \cdot t_{1} + a_{42} \cdot t_{2}$$

$$y_{1} = a_{43} \cdot x_{0} + a_{44} \cdot x_{1} + a_{45} \cdot x_{2} + a_{46} \cdot x_{3} + a_{47} \cdot t_{0} + a_{48} \cdot t_{1} + a_{49} \cdot t_{2}$$

$$y_{2} = a_{50} \cdot x_{0} + a_{51} \cdot x_{1} + a_{52} \cdot x_{2} + a_{53} \cdot x_{3} + a_{54} \cdot t_{0} + a_{55} \cdot t_{1} + a_{56} \cdot t_{2}$$

$$y_{3} = a_{57} \cdot x_{0} + a_{58} \cdot x_{1} + a_{59} \cdot x_{2} + a_{60} \cdot x_{3} + a_{61} \cdot t_{0} + a_{62} \cdot t_{1} + a_{63} \cdot t_{2}$$

This set of equations does not depend on f yet, but only on the values of n and m. The equations in C have to be satisfied for all possible S-box inputs. An equation set C' is created that contains  $2^n$  copies of the equations in C, in which all  $x_i$ ,  $y_i$ ,  $q_i$ ,  $t_i$  are renumbered, but in which all  $a_i$ ,  $b_i$  remain the same. f is *bound* to the problem description by adding its truth table as  $2^n(n+m)$  constant equations, i. e., one for every bit in both the S-box input and the S-box output, to C'.

*C'* is in ANF. The method by Bard, Courtois, and Jefferson [BCJ07] for converting sparse systems of low-degree multivariate binary polynomials is used to convert *C'* to CNF, such that it is understood by the SAT solver.

**Results.** This method makes it feasible to find the multiplicative complexity of several 4-bit and 5-bit S-boxes. Finding the multiplicative complexity comes with an actual implementation that uses this minimal number of nonlinear gates. After Courtois, Hulme, and Mourouzis applied this method to the S-boxes of PRESENT and GOST [CHM11], we show that we can also find results for more recently introduced 4-bit and 5-bit S-boxes.

We consider the S-boxes, and if applicable, their inverses (denoted by  $^{-1}$ ), in Ascon [DEMS16], ICEPOLE [MGH+14], Keccak [BDPV11b]/Ketje [BDP+16a]/Keyak [BDP+16b], all PRIMATES [ABB+14], Joltik [JNP15]/Piccolo [SIH+11], LAC [ZWW+14], Minalpher [STA+15], Prøst [KLL+14], and RECTANGLE [ZBL+14]. Minalpher's and Prøst's S-boxes are involutory, which is why their inverses are not listed separately. The inverse S-boxes in Ascon, ICEPOLE, Keccak, Ketje, and Keyak are not actually used in decryption and are therefore not considered.

For all S-boxes except the one used by the PRIMATEs we are able to prove the multiplicative complexity. The results are summarized in Table 3.1. The actual implementations can be found in the original publication [Sto16b], but note that these should most likely not be used by themselves as we are being very generous with XOR gates. The linear parts should be optimized separately, as we will demonstrate in Section 3.4.

These and subsequent results are obtained using MiniSat 2.2.0<sup>2</sup> and CryptoMiniSat 2.9.10<sup>3</sup> using default parameters on a single core of an Intel Xeon E7-4870 v2 running at 2.30 GHz.

<sup>2</sup> https://www.minisat.se/MiniSat.html

<sup>3</sup> https://www.msoos.org/cryptominisat2/

| S-box                                       | Size | Multiplicative complexity |

|---------------------------------------------|------|---------------------------|

| Ascon                                       | 5    | 5                         |

| ICEPOLE                                     | 5    | 6                         |

| Keccak/Ketje/Keyak                          | 5    | 5                         |

| PRIMATES                                    | 5    | ∈ {6,7}                   |

| PRIMATEs <sup>-1</sup>                      | 5    | $\in \{6, 7, 8, 9, 10\}$  |

| Joltik/Piccolo                              | 4    | 4                         |

| Joltik <sup>−1</sup> /Piccolo <sup>−1</sup> | 4    | 4                         |

| LAC                                         | 4    | 4                         |

| Minalpher                                   | 4    | 5                         |

| Prøst                                       | 4    | 4                         |

| RECTANGLE                                   | 4    | 4                         |

| RECTANGLE⁻¹                                 | 4    | 4                         |

**Table 3.1:** Multiplicative complexity of S-boxes.

For the PRIMATEs S-box and inverse S-box, we find solutions for k = 7 and k = 10, respectively. Furthermore, we find for both S-boxes that the case for k = 5 yields UNSAT. We have started several attempts to find a decisive answer for k = 6, including:

- ► reducing the CNF, e. g., using NICESAT [CMV09];

- ► fine-tuning SAT solver parameters;

- ► trying other SAT solvers;

- ► trying other SAT solvers that can run in parallel on many cores, such as Plingeling and Treengeling;<sup>4</sup> and

<sup>4</sup> http://fmv.jku.at/lingeling/

▶ letting all of this run for several months on a machine with 120 cores and 3 TB of RAM.

Unfortunately, none of these attempts resulted in an answer as no solver instance has terminated yet. As these SAT solvers typically have much more difficulty with proving the UNSAT case than proving the SAT case, and as the SAT proof for k = 7 was found in less than 40 hours, we expect the k = 6 case to yield UNSAT and we therefore conjecture the multiplicative complexity of the PRIMATEs S-box to be 7. In Section 3.4 we go into more detail on optimizing the PRIMATEs S-box. For the inverse S-box, we did not manage to find solutions for  $k \in \{6,7,8,9\}$ .

### 3.3.3 Optimizing for Bitslice Gate Complexity

In the same work [CMH13; Mou15], a method is given to optimize for bitslice gate complexity. However, it is only applied on the small CTC2 toy cipher and therefore it remains unclear how practical this method is for real-world ciphers. We investigate this by applying the method to the same S-boxes as in the previous section.

The encoding scheme for the bitslice-gate-complexity decision problem is slightly different compared to the multiplicative-complexity decision problem. Let  $f: \mathbb{F}_2^n \to \mathbb{F}_2^m$  again be an S-box and let k now be the bitslice gate complexity that we want to test for. Then our first set of equations C in ANF consists of:

- ▶  $\forall i \in \{0, ..., k-1\}$ :  $t_i = b_{3i} \cdot q_{2i} \cdot q_{2i+1} + b_{3i+1} \cdot q_{2i} + b_{3i+1} \cdot q_{2i+1} + b_{3i+2} + b_{3i+2} \cdot q_{2i}$ , to encode the k AND, OR, XOR or NOT gates. The  $b_i$  determine what kind of gate this will represent, as can be seen in Table 3.2.

- ▶  $\forall i \in \{0, ..., k-1\}$ :  $0 = b_{3i} \cdot b_{3i+2}$  and  $0 = b_{3i+1} \cdot b_{3i+2}$ , to make sure that the gate is either a unary NOT or a binary AND, OR, or XOR, but not one of them combined with a NOT. This excludes NAND, NOR, and XNOR gates.

- ▶  $\forall i \in \{0, ..., 2k-1\}$ :  $q_i = \left(\sum_{j=0}^{n-1} a_{l+j} \cdot x_j\right) + \left(\sum_{j=0}^{\lfloor \frac{i}{2} \rfloor 1} a_{l+n+j} \cdot t_j\right)$ , where  $l = in + \lfloor \frac{i^2 2i + 1}{4} \rfloor$ , to encode that the inputs of the gates can be any S-box input bit or any previously computed bit.

- ▶  $\forall i \in \{0, ..., 2k-1\}, \forall j \in \{l, ..., l+n+\lfloor \frac{i}{2} \rfloor -2\}, \forall u \in \{j+1, ..., l+n+\lfloor \frac{i}{2} \rfloor -1\}$ :  $0 = a_j \cdot a_u$ , to encode an *at-most-one* constraint on the gate inputs.

- ▶  $\forall i \in \{0, ..., m-1\}$ :  $y_i = \left(\sum_{j=0}^{n-1} a_{s+j} \cdot x_j\right) + \left(\sum_{j=0}^{k-1} a_{s+n+j} \cdot t_j\right)$ , where s = 2kn + k(k-1) + i(n+k), to encode that the S-box output bit can be any S-box input bit or any gate output.

- ▶  $\forall i \in \{0, ..., m-1\}, \forall j \in \{s, ..., s+n+k-2\}, \forall u \in \{j+1, ..., s+n+k-1\}:$ 0 =  $a_j \cdot a_u$ , to encode an *at-most-one* constraint on the S-box outputs.

**Table 3.2:** Gate modifiers for bitslice gate complexity.

| $b_{3i}b_{3i+1}b_{3i+2}$ | Gate $t_i$ function                   |

|--------------------------|---------------------------------------|

| 000                      | 0                                     |

| 001                      | $\neg q_{2i}$                         |

| 010                      | $q_{2i} \oplus q_{2i+1}$              |

| 011                      | Prevented by constraint on $b_{3i+2}$ |

| 100                      | $q_{2i} \wedge q_{2i+1}$              |

| 101                      | Prevented by constraint on $b_{3i+2}$ |

| 110                      | $q_{2i} \vee q_{2i+1}$                |

| 111                      | Prevented by constraint on $b_{3i+2}$ |

Converting C to C' and then to CNF is the same process as with the multiplicative-complexity decision problem. Note that the constraint equations on  $a_i$  and  $b_j$  do not have to be duplicated  $2^n$  times for C', as they are not renumbered. This saves a lot of redundant clauses.

**Results.** As the amount of CNF clauses that is necessary to describe the bitslice-gate-complexity decision problem becomes much larger compared to the multiplicative-complexity decision problem, it can take much more time for a SAT solver to actually solve a problem instance. Still, for some 4-bit and 5-bit S-boxes results can be obtained within minutes or within a few hours. Table 3.3 contains some examples. If a bitslice gate complexity is listed as  $\leq k$ , a solution was found for k, but we were unable to prove that this is the minimum because the SAT solver did not terminate within a reasonable amount of time for k-1. Similarly, in some cases a lower bound was found because the SAT solver was able to determine that no circuit exists with that numbers of gates. The actual implementations with the given number of operations can be found in the original publication [Sto16b].

**Table 3.3:** Bitslice gate complexity of S-boxes.

| S-box                                       | Size | Bitslice gate complexity | Implementation            |

|---------------------------------------------|------|--------------------------|---------------------------|

| Keccak/Ketje/Keyak                          | 5    | ≤ 13                     | 3 AND, 2 OR, 5 XOR, 3 NOT |

| Joltik/Piccolo                              | 4    | 10                       | 1 AND, 3 OR, 4 XOR, 2 NOT |

| Joltik <sup>−1</sup> /Piccolo <sup>−1</sup> | 4    | 10                       | 1 and, 3 or, 4 xor, 2 not |

| LAC                                         | 4    | 11                       | 2 AND, 2 OR, 6 XOR, 1 NOT |

| Minalpher                                   | 4    | ≥ 11                     |                           |

| Prøst                                       | 4    | 8                        | 4 AND, 4 XOR              |

| RECTANGLE                                   | 4    | $\in \{10, 11, 12\}$     | 4  OR, 7  XOR, 1  NOT     |

| RECTANGLE <sup>-1</sup>                     | 4    | ∈ {11, 12}               | 1 AND, 3 OR, 7 XOR, 1 NOT |

For Prøst, it is interesting to note that the SAT solvers are able to find the same implementations as its authors already suggested. We have proven that their bitsliced implementation is indeed minimal.

## 3.3.4 Optimizing for Gate Complexity

A method to encode the gate-complexity decision problem was also provided by Courtois, Mourouzis, and Hulme [CMH13; Mou15], but again, actual results were only given for the CTC2 toy cipher. We show that it is feasible to compute the gate complexity for real-world 4-bit S-boxes as well.

The encoding is very similar to the bitslice-gate-complexity decision problem. The first set of equations *C* in ANF only differs in two places: